Studies

Studies

For all who are interested in my study, here is a little overview of lectures/labs/seminars I attended till now during my study of computer science at the University of Karlsruhe, from 10/2003 to 12/2008.

(Note: I tried to translate the name of the german lecture names as precise as I cannot guarantee that the translation is correct. But I hope you can somehow imagine what it's about...)| Subject | Lecturer | SWS |

| Informatics I | Goos | 4+2 |

| Linear Algebra and Analytic Geometrics I | Kühnlein | 4+2 |

| Higher Mathematics I (Analysis I) | Schmoeger | 4+2 |

| Basics of Theory of Probability and Statistics | Klar | 2+1 |

| Informatics II | Zitterbart | 4+2 |

| Linear Algebra and Analytic Geometrics II | Kühnlein | 2+1 |

| Higher Mathematics II (Analysis II) | Schmoeger | 5+2 |

| Physics I for Computer Scientists | Blümer | 3+1 |

| Numerical Mathematics | Scherer | 2+1 |

| Informatics III | Wagner | 4+2 |

| Computer Engineering I | Asfour | 3+1 |

| Physics II for Computer Scientists | Blümer | 3+1 |

| System Architecture (Practical Work) | Liefläder | - |

| Informatics IV | Schmitt | 4+2 |

| Computer Engineering II | Brinkschulte | 3+1 |

| Electrical Engineering for Computer Scientists | Crocoll | 2+0 |

| System Architecture | Liefländer | 4+2 |

| Software Engineering | Tichy | 4 |

| Formal Systems (Logic) | Schmitt | 4 |

| Algorithm Engineering | Wagner | 4 |

| Lab "Lego Mindstorm" | ITEC Dillman | - |

| Cognitive Systems | Dillmann/Waibel | 4 |

| Computer Architecture | Karl | 4 |

| Real-Time Systems | Brinkschulte | 4 |

| Introduction to .NET | Tichy | 2 |

| Seminar "Modern Software Engineering" | FZI | - |

| Embedded Systems I | Feldbusch | 2 |

| Embedded Systems II | Henkel | 2 |

| Microprocessors for Embedded Systems | Karl | 2 |

| Parallel Architectures and Programming | Tao | 2 |

| Software-Engineering for Embedded Systems | FZI | - |

| Embedded Security | Lazic | 1 |

| Automotive Engineering I | Unrau | 4 |

| Automotive Mechatronics I | Ammon | 2 |

| Lab "Design of Embedded Application-Specific Processors" | CES | - |

| Signals, Codes & Chiffres I | Lazic | 3 |

| Signals, Codes & Chiffres II | Geiselmann | 3+1 |

| Quanta Cryptography | Müller-Quade | 2 |

| Fundamentals of Computer Security | Röhric | 2 |

| Curves and Areas in CAD | Prautzsch/Chen | 4 |

| Graphical-Geometrical Algorithms | Bender | 2 |

| Communication & Databases | Abeck/Buchmann | 4+1 |

| Automotive Engineering II | Unrau | 2 |

| Intelligent Data Analysis | Feldbusch | 2 |

| Tutor for Informatics IV | - | - |

| Applied Differential Geometry | Prautzsch | 2 |

| Automatic Visual Inspection and Image Processing | Beyerer | 4 |

| Nets and Point Clouds | Prautzsch | 2 |

| Introduction to Graphical Data Processing | Preuß | 2 |

| Introduction to Multimedia | Deussen | 2 |

Tutor for Informatics I (1x Tutorial + 2x Computer Exercise Lessons per week).Therefore exists my own tutorial homepage: Informatics I Tutorial 24 Winter Term 07/08

Informatics I Tutorial 24 Winter Term 07/08

|

- | - |

| Study Thesis at the Institute of Computer Science & Engineering: Thesis: Implementation of a Monitoring Unit for the Hypertransport Bus System |

Buchty | - |

|

Diploma Thesis at the Chair for Embedded Systems: "Development of a Power-Aware Rate Controller for the H.264 Video Encoder". Click here for further details. |

Henkel, Shafique | - |

The exercise was realised in a team of three students. Everyone had to build a roadworthy robot (well, playing lego can be really fun :-) The main assignment was of course the engineering of the software: in a special zoned area there were several 'stations' of form of straps on the floor. Each robot had to pass at least one of these stations once (they had light sensors at their undersides). After that they had to find their way home and park there. The most difficult job was the implementation of the communication per infrared between the three robots: they had to decide themselves which robot(s) visit(s) the non-passed station(s). At the end they had to meet again in the house and shut down themselves. We took special care for paricular cases (what should happen of one or more robots drop out?). We coded in NQC.

In summer term 06, I attended the seminar 'Modern Software Engineering' at the Research Center of Information Technologies and worked out an elaboration and a presentation of the topic "Generative Programming". Only in German available.

Downloads:

Composition (PDF, 200kb)

Presentation (PDF, 90kb)

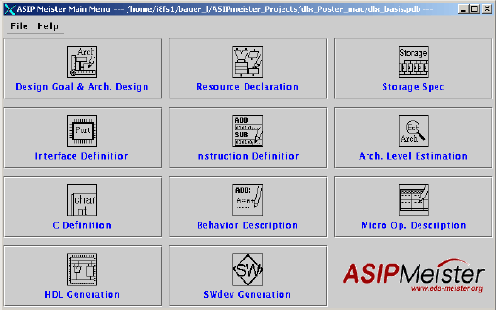

In this laboratory

we implemented special instructions directly in hardware, among other things

a compare-instruction (which not existed yet in the instruction set) or an instruction

which calculated the hamming distance of two 32 bit words. With ASIPMeister,

we defined new instructions, new instruction types and complete new functional

units (in VHDL) and designed their behaviour in the single pipeline stages.

After the automatic synthesis we tested our results in ModelSim and on a Xilinx

FPGA board. For estimations (like power consumption or chip area) we used Xilinx

ISE.

The speed difference beween the software

implementation and the hardware one is extreme.

More information is available here.

Slides with the result of our last project are available here (1,7MB).

In winter term 07/08 I completed succesfully my study thesis at the Institute for Computer Engineering (Chair Prof. Karl).

I was provided with the HTX-Board (a FPGA with a Virtex FX-100 with HyperTransport Interface) in an AMD Athlon-System

and the so-called HT-Core - a HyperTransport device available as Verilog Source, synthezisable with Xilinx

ISE. Starting form this, my challenge was to create a monitoring unit in VHDL

which logs all read and write accesses using the HyperTransport Bus in a content-addressable

memory. If the memory is full, all logged information should be send to a buffer

in main memory and from there saved to a file for further analysis. Therefore

I had to use a kernel driver which allocated a non-cachable DMA region und sent

its physical address to the board. I programmed a usel-level application in

C under Linux which executes several read and writes accesses on the board (resp.

on the mapped board memory) and saved all logged infos to file.

Especially

difficult was the linkage to the HyperTransport bus system cause there was no

real simulation option available, the synthesis and upload to the board lasted

nearly an hour and even very small bugs caused the system to hang during startup

because the board was not properly recognized as a PCI device. Also by executing

board accesses there were often problems....

HTX Board

In June 2008, I started my diploma thesis at the the Chair for Embedded Systems (Prof. Henkel) with the title

"Development of a Power-Aware Rate Controller for H.264 Video Encoder" -

consisting of diving into the hot multimedia topic video encoding (and H.264 is quite complicating),

changing the existing Rate Controller and Rate-Distortion-Optimization by improving their computational complexity while not loosing too much quality,

coding my changes into the Reference Software (Open source, in C) and finally

porting my algorithms to a FPGA.

I must admit the beginning was not that easy and it took some time till I really understood the whole encoding process,

especially the Lagrangina Optimization and the models used in Rate Controller, but my attempt pointed out to work extremely nice:

I achieved a significant speedup by predicting the encoding modes exploiting image statistics analysis on the video frames.

My PID-based Rate Controller also prioritize more important (=textured with motion) regions than background area, resulting in better subjective quality.

In fact, I really did many modifications and I am absolutely proud of my diploma thesis.

Update: I am not allowed to publish my diploma thesis here, but have a look at the two linked papers below - in fact they are some sort of summary of my thesis!

Diploma Thesis Flyer (PDF, 250kb)

Diploma Thesis Flyer (PDF, 250kb)

Diploma Thesis: Table of Contents (PDF, 150kb)

Diploma Thesis: Table of Contents (PDF, 150kb)

Received the FZI Prize (Forschungszentrum für Informatik) for Best Diploma Thesis Award!

Received the FZI Prize (Forschungszentrum für Informatik) for Best Diploma Thesis Award!

My thesis was the base of two published articles (see my mentor's page for more information):

My thesis was the base of two published articles (see my mentor's page for more information):

Muhammad Shafique, Bastian Molkenthin, Jörg Henkel:

Non-Linear Rate Control for H.264/AVC Video Encoder with Multiple Picture Types using Image-Statistics and Motion-Based Macroblock Prioritization

IEEE 16th International Conference on Image Processing (ICIP´09)

Cairo, Egypt, November 2009

pp. 3429-3432

Download Paper from Server of University of Karlsruhe (pdf ~536 KB)

Muhammad Shafique, Bastian Molkenthin, Jörg Henkel:

An HVS-based Adaptive Computational Complexity Reduction Scheme for H.264/AVC Video Encoder using Prognostic Early Mode Exclusion

IEEE/ACM 13th Design Automation and Test in Europe Conference (DATE´10)

Dresden, Germany, March 2010

pp. 1713-1718

Download Paper from Server of University of Karlsruhe (pdf ~935 KB)

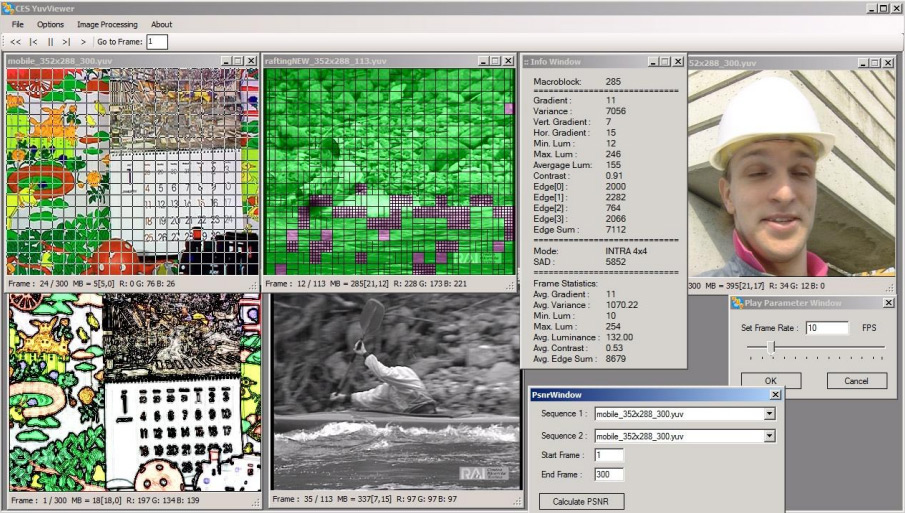

Below you see a picture of my tool I called YuvViewer. It's just a spin-off product I coded myself in the evenings during my diploma thesis (yes, that's correct, it's not an official part of my thesis!). The reason was that I needed a comfortable and fast way to investigate the image & motion characterics of a large set of videos (in 4:2:0 YUV format).

YuvViewer offers multiple useful features combined in one application: many sequences can be opened and played at the same time (even synchronically). An information window can be activated to show the macroblock image statistics under the current cursor position in real-time (beside frame statistics). This information can be also saved to a text file. Sequences can be altered, e.g. the edge map can be displayed and/or only the luminance component. Noisy, blurred, darken and brighten sequences have also been generated with this tool. (Altered) sequences can be party or wholly saved to new .yuv sequences. An implemented modification into the H.264 reference software saves the chosen mode for each macroblock along with its SAD value to a file. This file can be loaded by YuvViewer and examined on the fly. Additional features include zooming of sequences, computing the PSNR value per frame of two sequences and setting the playback frame rate.

It was coded in C# and requires therefore Windows XP or Windows Vista with an installed .Net framework (Version 2.0 or higher). Unfortunately I am not allowed to publish source or binary.

This site is part of Sunshine's Homepage